SFP+ PASSIVE L=3M RL在9.5G-10G不过,提供截图,帮忙分析。 - 简版

chenwei259

楼主

2011-09-13 22:00:00

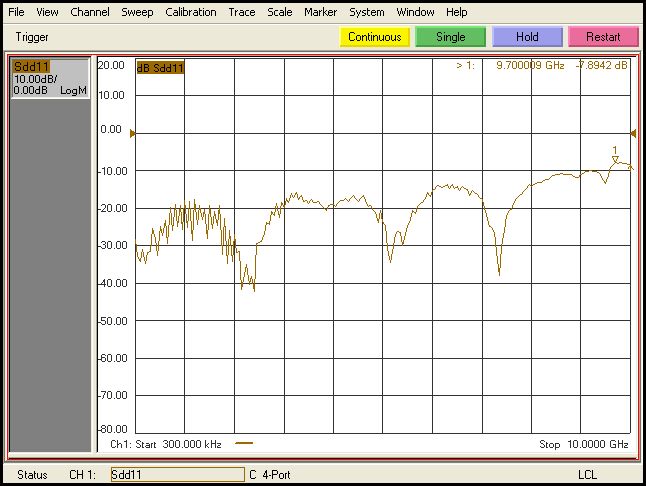

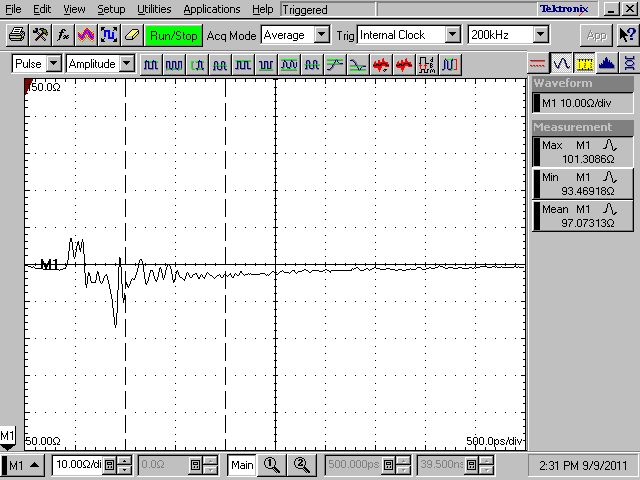

SFP+ PASSIVE L=3M, Return loss:<-10dB 300khz-10GHZ,测试4PCS样品均在9.5G-10G不过,而且最高点都在9.8G。

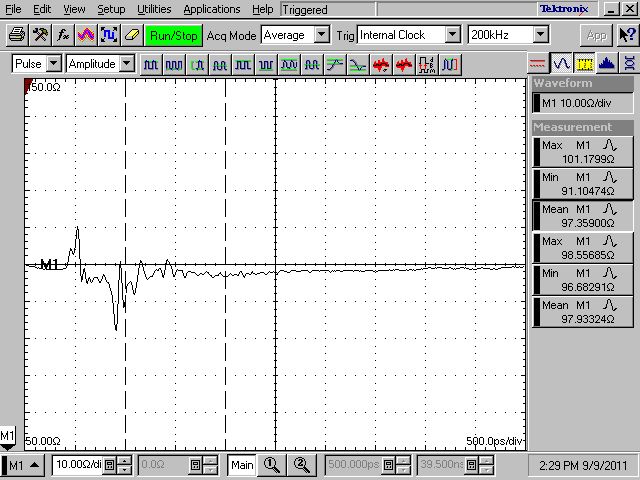

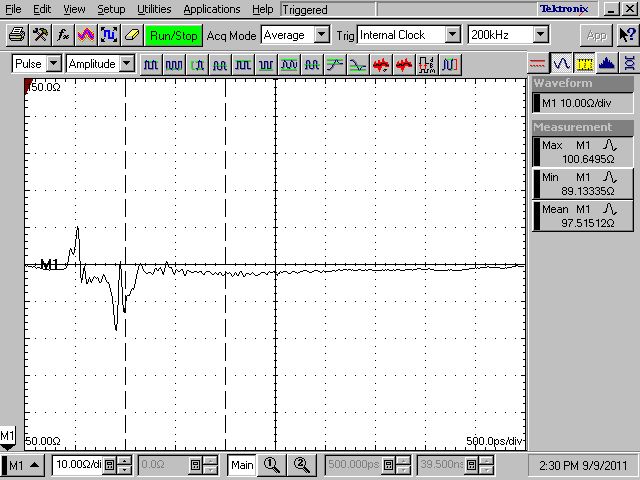

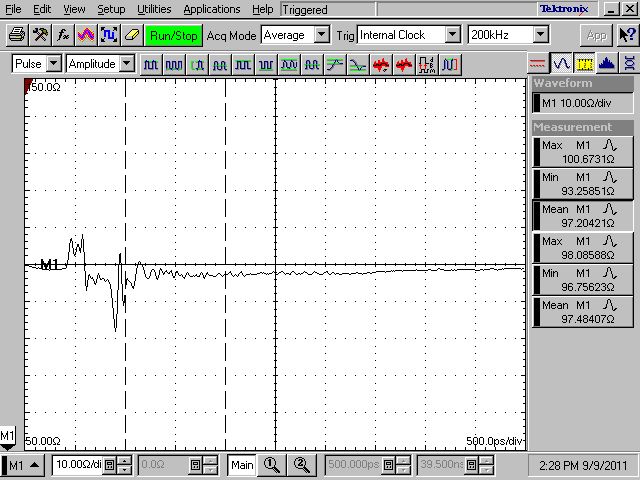

IMPEDANCE都在规格内,波形也还正常,但全部偏下限,焊点92ohm以下。

但上次测试过了,最大-12.4dB,焊点控制在94ohm以上。

目前对策是:加工时将焊点阻抗拉高,另外测试板阻抗也不太好,打算弄个新的测试板,不知大家有什么高见?

sample1 /pair1/SDD11

sample1 /pair2/SDD11

sample1 /pair1/ConnA+Cable/IMPEDANCE

sample1 /pair1/ConnB/IMPEDANCE

sample1 /pair2/ConnA+Cable/IMPEDANCE

sample1 /pair2/ConnB/IMPEDANCE

dedyqi

1 楼

2011-09-14 09:28:02

看不懂

卓一航

2 楼

2011-09-14 10:02:13

昆山能做这个线的也没几家。。。你是不是裸线本身就有问题呢?

mudong

3 楼

2011-09-14 11:15:03

图是真看不懂

chenwei259

4 楼

2011-09-14 18:26:01

大家给点意见,解决后会一起分享经验,如何?

目前进度:准备先测RAW CABLE和PCB再做成品。

killer555

5 楼

2011-09-16 11:06:50

什么是SFP?

泡泡

6 楼

2011-09-16 16:43:59

QSFP(Quad Small Form-factor Pluggable):四通道SPF接口(QSFP),QSFP是为了满足市场对更高密度的高速可插拔解决方案的需求而诞生的。 <DIV class=spctrl></DIV> 这种4通道的可插拔接口传输速率达到了40Gbps。很多XFP中成熟的关键技术都应用到了该设计中。 <DIV class=spctrl></DIV> QSFP可以作为一种光纤解决方案,并且速度和密度均优于4通道CX4接口。由于可在XFP相同的端口体积下以每通道10Gbps的速度支持四个通道的数据传输,所以QSFP的密度可以达到XFP产品的4倍,SFP+产品的3倍。具有4通道且密度比CX4高的QSFP接口已经被InfiniBand标准所采用。

泡泡

7 楼

2011-09-16 16:46:09

楼主,并线重叠有多少

shoulei

8 楼

2012-04-23 19:58:55

阻抗做上限效果是否会好些呢?

晨曦1394

9 楼

2012-04-25 12:24:56

從圖形來看這個阻抗有些偏低,建議做到100~~105歐姆

guangxi

10 楼

2012-04-30 21:52:37

我们公司也做SFP+,SFP,QSFP,SAS,

头端阻抗有点偏低,再换个测试板阻抗高点的试,

lange

11 楼

2012-05-20 12:44:33

pull

12 楼

2012-05-31 08:56:01

这个肯定是加工时造成的,裸线和连接器不用测了。

FlyFu

13 楼

2012-05-31 17:23:44

阻抗片底造成的,成品阻抗不小于95歐姆应该可以做到。

lange

14 楼

2012-07-11 17:04:29

jimwang

15 楼

2012-07-11 22:03:58

还需要详细的说明

274262832

16 楼

2012-07-12 16:16:24

楼主芯线绝缘是什么材质

李小龍

17 楼

2012-07-12 18:06:59

阻抗为什么你要做片下限呢?RL要好,还是要做到匹配尽量好的点上去,所以,调高点阻抗,尽量平稳到100左右吧

Cable1982

18 楼

2012-07-18 23:18:13

支持小龙兄!RL要好阻抗不是高点好,而是要匹配。尽可能做到接近100欧姆越接近越好。