Namisoft����PXI���ߵĿ���Ƶ�ʼ���� - ���

Ƶ���źž��п�������ǿ�����ڴ��䣬���ڱ�����Ϣ�����ԺͿ��Ի�ýϸ߲������ȵ��ŵ㣬���㷺Ӧ�����ճ������ҵ�ȸ�������Ƶ�ʲ�����Ϊ��Ϣ��ȡ���豸���ȹ����е�һ����Ҫ���ڡ�Ƶ�ʼ����Ϊ���Ӳ�������������IJ���֮һ���������ֵ��Ӽ����ķ�չ���õ��˳���Ľ���������Ƶ�ʲ���Ҳ�õ���Խ��Խ�㷺��Ӧ�ã��Ӷ�ʹ��Ƶԭ���Ͳ�Ƶ�������о��ܵ�Խ��Խ��Ĺ�ע������������Ƶ�ʲ���ԭ���ͷ����Ļ����ϣ���Ҫ����һ�ֻ���PXI���ߵĿ������߾�������Ƶ�ʼƵ������ʵ�֡�

1��Ƶԭ��

Ŀǰ��Ƶ�ʵIJ������õķ�����Ҫ�У�Χ�Ƶ��Ӽ�������һ��ʱ���ڵ����������ȷ��Ƶ��;���ź�ʱƵ�任���㷨�����о���������Ҫ����ǰ�ߡ�

1.1ֱ�Ӳ�Ƶ��

���Ӽ�������һ�����ñȽϷ����в��������������������ֻ����������������ֻ������Ļ�����Ƶ����ʱ����������������ģ���˶�Ƶ�ʲ�����Ҫȷ��һ��ȡ��ʱ��T���ڸ�ʱ���ڶԱ����źŵ����ڽ����ۼӼ���(������ֵΪN)������fx=N/T�õ�Ƶ��ֵ�����ַ�������բ��ʱ���뱻���źŲ�ͬ��������ʱ���ڡ�1�ļ�����Ӱ���Ƶ���ȡ�

1.2�Ⱦ��Ȳ�����

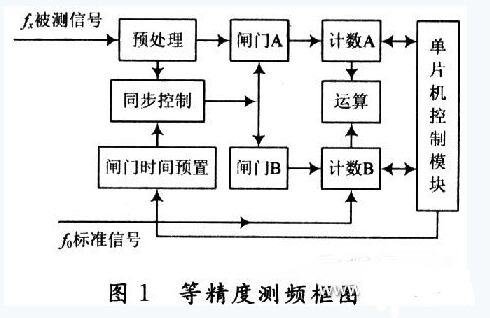

�ɼ�ֱ�Ӳ�Ƶ����Ȼ��Ƽ����Ǿ��Ȳ��ߣ�Ϊ��������1��������������иĽ���ͼ1��ʾ��

�����źž����˲����Ŵ�Ƶ������Ԥ����֮��������ķ����źź�բ��ʱ��Ԥ�÷����źŽ���ͬ�����ơ�ͬ������һ����D����������̬����ʵ�֡��ڲ�Ƶ�ʺ�����ʱ����Ƭ���������ķ��������ź�ʹ��̬�����Ŵ��ڸ���״̬��ͬʱ��������բ���źţ��������ź����κ�ķ����ź������ص���ʱ��ͬ�����Ʒ����źţ�ʹբ��A��բ��Bͬʱ��ʼ�Ա����źźͱ��źŽ��м���������Ƭ����������բ���źź�fx�ķ����ź������صĵ�������ʹ������ֹͣ�������������жϷ���������ʵ����բ�ŵ�������fxͬ�����ٽ��жϷ������������������������Ľ��д���������������ʾϵͳ����ʾ���������ʱ��ͼ��ͼ2��ʾ��

�������������Ҫ���Ա�Ƶ�ź���բ��B��ͬ�������ġ���1����Ϊ��һ����߲�Ƶ���ȣ�����˻�����λ�غϵ�ȫͬ����Ƶ������

1.3ȫͬ����Ƶ��

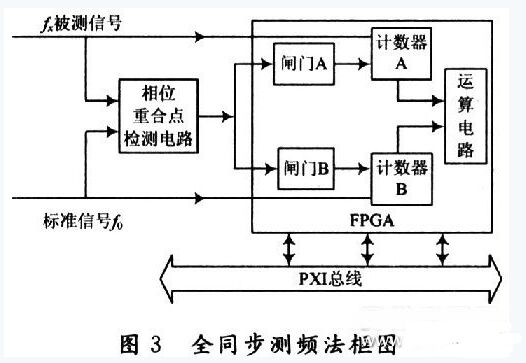

ȫͬ��Ƶ�ʼƲ�Ƶ˼·�������ź�fx��������·���������Ƶ��f0һ��������λ�غϵ����·���ȿ���Ԥ��բ�ţ������������������ź���λ��һ���غ�ʱ��ʵ��բ�Ų���ʼ��������ʵ��բ�ŵĹر�����Ԥ��բ���½��غ�ĵ�һ����λ�غϵ㵽��ʱ�رյġ�������������·��1s�����ۻ�11���������������Ƶ�����塣Ƶ�ʼ��㹫ʽ�Ⱦ��Ȳ�Ƶһ����������Ϊ����Ƶ�ʡ���Ƶ����բ�Ŵﵽ��������һ�£������ϳ��������ˡ�1�ļ�������ͼ3��ʾ��

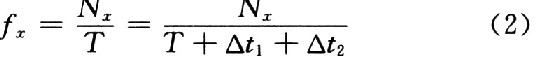

�迪��բ��ʱ����ͬ��ʱ���Ϊ��t1���ر�բ��ʱ����ͬ��ʱ���Ϊ��t2���������λͬ�����������Ϊ��t������ ��t1�ܡ�t����t2�ܡ�t�����Ʊ�ʱ����ʵ��բ�����ʱ��ͬ����ʵ��բ��ʱ��ΪT�������źż���ֵΪNx����ʱ�Ӽ���ֵΪNo�����źŵ�Ƶ�ʲ���ֵΪ��

��ʵֵΪ��

Ƶ�ʲ�����������Ϊ��

��ʽ(3)��֪�����ֻ��������λ����·��ȷ���йء�

2Ӳ����·���

2.1�źŵ�����·���

�����ź�Ϊ1Hz��6GHz��Ƶ����Χ�Ͽ�����CPLD/NSAT-2000����Ԫ����FPGA�м���������Ƶ�ʲ�����200MHz�������Ҫ�Ա����źŽ���Ԥ��������Ƶ�ʼ�ģ�����3������ͨ�����ֱ�Ϊ0��1��2ͨ�������У�Oͨ������Ƶ�ʷ�ΧΪ 1��6GHz;1ͨ������Ƶ�ʷ�ΧΪ50MHz��1GHz;2ͨ������Ƶ�ʷ�ΧΪ1Hz��50MHz������0��1ͨ�����źţ�����Ƶ�ʽϸߣ�������ɸ�Ƶ�źŽ��������н������Σ�Ȼ��ǰ�˷�Ƶ����Ƶ���͵�NSAT-2000����Ԫ����FPGA/CP-LD���м���;����2ͨ��������źű��Ŵ����κ�ֱ���͵�NSAT-2000����Ԫ����FPGA/CPLD������

2.2����ѡ��

���ڸ�Ƶ�ʼ�ģ���3������ͨ������Ӧ��ͬ�IJ���ͨ����ѡ�������Ӧ����������Oͨ����ѡ��ZL40800�� SP8782��ʵ��8��32��Ƶ;��1ͨ����ѡ��SP8782ʵ��32��Ƶ;��2ͨ��ѡ��ʩ���ش��������źŽ��зŴ����Ρ����ȶ��Ⱦ���ѡ��TC75�¶Ȳ����������ȶ���Ϊ��10-8;NSAT-2000����Ԫ����FPGAѡ������������EPM7032SLC44-5�����ٶȵȼ�Ϊ5ns���������˸õ�·��Ҫ���ּ���˵�ż���;��Ƶ�źŽ���������NB6L16��ֽ�����������յ�����ź�Ƶ�ʿɴ�6GHz��

2.3PXI���߽ӿڵ�·���

ר��PCI�ӿ�оƬ��CPLD/NSAT-2000����Ԫ����FPGA�Ľӿڷ���������ר�ýӿ�оƬPCI9030��û����ֱ�Ӳ���CPLD/NSAT-2000����Ԫ����FPGA��ô���������Դ�����̿������ڣ�����ר�����߽ӿ�оƬ����ͨ���ԣ��ṩ���üĴ������߱�����ͻ�����书�ܵ�Ƭ��FIFO���ŵ㣬�������������PXI���߽�����������������Ͷ�뵽��������֤��ʱ����������ϣ��������ڳ��ıˡ�

2.4����NSAT-2000����Ԫ����FPGA����λ�غϼ���·���

��λ�غϼ���·����ԭ��������NSAT-2000����Ԫ����NSAT-2000����Ԫ����FPGA�ڲ�����ʱ���ԣ��źž���������ʱ���ԭ�ź����룬���ɻ������ʱʱ�䳤����ͬ���������������Ϊ���Ե����ڣ�����·�ź��ڵ�һ������֮���غ�ʱ��y����ߵ�ƽ����ʱ�ж����ź���λ�غϡ�EPM7032SLCA4-5����ʱʱ��Ϊ5ns��